# AS4C128M16D2

# 128M x 16 bit DDRII Synchronous DRAM (SDRAM)

Confidential Advanced (Rev. 1.0, Mar. /2014)

#### **Features**

- High speed data transfer rates with system frequency up to 400 MHz

- 8 internal banks for concurrent operation

- 4-bit prefetch architecture

- Programmable CAS Latency: 3, 4,5, 6 and 7

- Programmable Additive Latency: 0, 1, 2, 3, 4, 5 and 6

- Write Latency = Read Latency -1

- Programmable Wrap Sequence: Sequential or Interleave

- Programmable Burst Length: 4 and 8

- Automatic and Controlled Precharge Command

- Power Down Mode

- Auto Refresh and Self Refresh

- Refresh Interval: 7.8 us (8192 cycles/64 ms) Tcase between 0°C and 85°C

- ODT (On-Die Termination)

- Weak Strength Data-Output Driver Option

- Bidirectional differential Data Strobe (Single-ended data-strobe is an optional feature)

- On-Chip DLL aligns DQ and DQs transitions with CK transitions

- DQS can be disabled for single-ended data strobe

- Differential clock inputs CK and CK

- JEDEC Power Supply  $1.8V \pm 0.1V$

- VDDQ =1.8V ± 0.1V

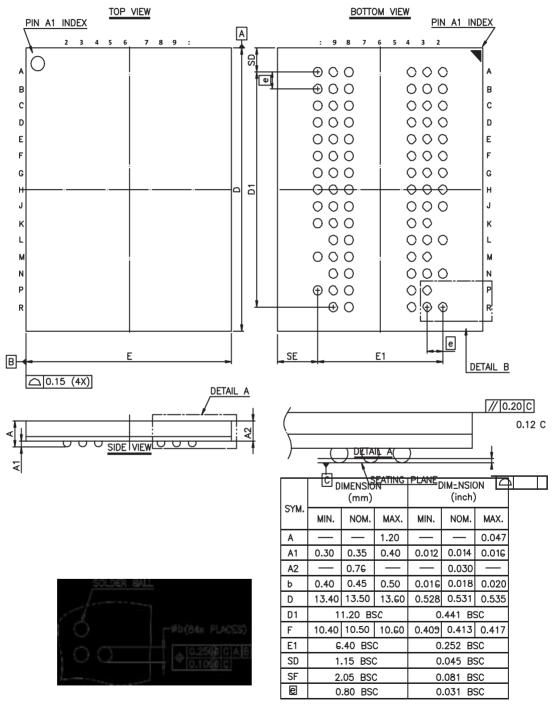

- Available in 84-ball FBGA

- RoHS compliant

- PASR Partial Array Self Refresh

- tRAS lockout supported

# Description

The AS4C128M16D2 is an eight bank DDR DRAM organized as 8 banks x 16Mbit x 16. The AS4C128M16D2 achieves high speed data transfer rates by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock.

The chip is designed to comply with the following key DDR2 SDRAM features:(1) posted CAS with additive latency, (2) write latency = read latency-1, (3) On Die Termination.

All of the control, address, circuits are synchronized with the positive edge of an externally supplied clock. I/O s are <a href="synchronized">synchronized</a> with a pair of bidirectional strobes (DQS, DQS) in a source synchronous fashion.

Operating the eight memory banks in an interleaved fashion allows random access operation to occur at a higher rate than is possible with standard DRAMs. A sequential and gapless data rate is possible depending on burst length, CAS latency and speed grade of the device.

# Table 1. Ordering Information

|   | Part Number       | Clock Frequency | Data Rate   | Power Supply        | Package     |

|---|-------------------|-----------------|-------------|---------------------|-------------|

| Α | S4C128M16D2-25BCN | 400MHz          | 800Mbps/pin | VDD 1.8V, VDDQ 1.8V | 84ball FBGA |

| Α | S4C128M16D2-25BIN | 400MHz          | 800Mbps/pin | VDD 1.8V, VDDQ 1.8V | 84ball FBGA |

B: indicates 84-ball FBGA package

C: indicates commercial temperature

I: indicates industrial temperature

N: indicates Pb and Halogen Free ROHS

# **Table 2. Speed Grade Information**

| Speed Grade | Clock Frequency | CAS Latency | t <sub>RCD</sub> (ns) | t <sub>RP</sub> (ns) |

|-------------|-----------------|-------------|-----------------------|----------------------|

| DDR2-800    | 400 MHz         | 5           | 5                     | 5                    |

1

# 2Gb DDR2 SDRAM Addressing

| Configuration  | 128Mb x 16 |

|----------------|------------|

| # of Bank      | 8          |

| Bank Address   | BAO ~ BA2  |

| Auto precharge | A10/AP     |

| Row Address    | A0~A13     |

| Column Address | A0 ~ A9    |

#### 128Mx16 DDR2 PIN CONFIGURATION

(Top view: see balls through package)

| 1    | 2      | 3    |   | 7     | 8         | 9    |

|------|--------|------|---|-------|-----------|------|

| VDD  | NC     | VSS  | Α | VSS Q | UDQS      | VDDQ |

| DQ14 | VSSQ   | UDM  | В | UDQS  | VS SQ     | DQ15 |

| VDDQ | DQ9    | VDDQ | С | VDD Q | DQ8       | VDDQ |

| DQ12 | VSSQ   | DQ11 | D | DQ10  | VS SQ     | DQ13 |

| VDD  | NC     | VSS  | Е | VSS Q | LDQS      | VDDQ |

| DQ6  | VSSQ   | LDM  | F | LD QS | VS SQ     | DQ7  |

| VDDQ | DQ1    | VDDQ | G | VDD Q | DQ0       | VDDQ |

| DQ4  | VSSQ   | DQ3  | Н | DQ2   | VS SQ     | DQ5  |

| VDDL | VRE F  | VSS  | J | VSSDL | CK        | VDD  |

|      | CKE    | WE   | K | RAS   | CK        | ODT  |

| BA2  | BA 0   | BA1  | L | CAS   | <u>cs</u> |      |

|      | A10/AP | A1   | М | A2    | A0        | VDD  |

| VSS  | A3     | A5   | N | A6    | A4        |      |

|      | A7     | A9   | Р | A11   | A8        | VSS  |

| VDD  | A12    | NC   | R | NC    | A13       |      |

# Signal Pin Description

| Pin                              | Type             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK                           | Input            | The system clock input. All inputs except DQs and DMs are sampled on the rising edge of CK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CKE                              | Input            | Activates the CK signal when high and deactivates the CK signal when low, thereby initiates either the<br>Power Down mode, or the Self Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| cs                               | Input            | CS enables the command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAS, CAS, WE                     | Input            | When sampled at the positive rising edge of the clock, CAS, RAS, and WE define the command to be executed by the SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A0 - A13                         | Input            | During a Bank Activate command cycle, A0-A13 defines the row address (RA0-RA13) when sampled at the rising clock edge.  During a Read or Write command cycle, A0-A9 defines the column address (CA0-CA9) when sampled at the rising clock edge.  In addition to the column address, A10(-AP) is used to invoke autoprecharge operation at the end of the burst read or write cycle. If A10 is high, autoprecharge is selected and BA0, BA1, BA2 defines the bank to be precharge of the A10 is low, autoprecharge is disabled.  During a Precharge command cycle, A10(-AP) is used in conjunction with BA0, BA1 and BA2 to control which bank(s) to precharge. If A10 is high, all eight banks will be precharged simultaneously regardless of state of BA0, BA1 and BA2. |

| BAD-BA2                          | Input            | Selects which bank is to be active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DQx                              | Input/<br>Output | Data Input/Output pins operate in the same manner as on conventional DRAMs.  DQ0-DQ15 for x16 component.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LDQS, <u>LDQS,</u><br>UDQS, UDQS | Input/<br>Output | Data Strobe, output with read data, input with write data. Edge-aligned with read data, centered in write data. For x16 component, LDQS corresponds to the data on DQ0-DQ7; UDQS coresponds to the data on DQ8-DQ15. The data strobes LDQS and UDQS may be used in single ended mode or paired with optional complimentary signals \overline{LDQS} and \overline{UDQS} to provide differential pair signaling to the system during both reads and writes. An EMRS(1) control bit enables or disables all complementary data strobe signals.                                                                                                                                                                                                                               |

| LDM, UDM                         | Input            | DM is an input mask signal for write data. Input data is masked when DM is sampled high along with that input data during a Write access. DM is sampled on both edges of DQS.  Although DM pins are input only, the DM loading is designed to match that of DQ and DQS pins.  LDM is DM for lower byte DQ0-DQ7 and UDM is DM for upper byte DQ8-DQ15.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDD, VSS                         | Supply           | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VDDQ, VSSQ                       | Supply           | Isolated power supply and ground for the output buffers to provide improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VREF                             | Input            | SSTL Reference Voltage for inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VDDL, VSSDL                      | Supply           | Isolated power supply and ground for the DLL to provide improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ODT                              | Input            | On Die Termination Enable. It enables termination resistance internal to the DRAM. For x16 configuration, ODT is applied to each DQ, UDQS/UDQS, LDQS/LDQS, UDM and LDM signal. ODT will be ignored if EMRS disable the function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

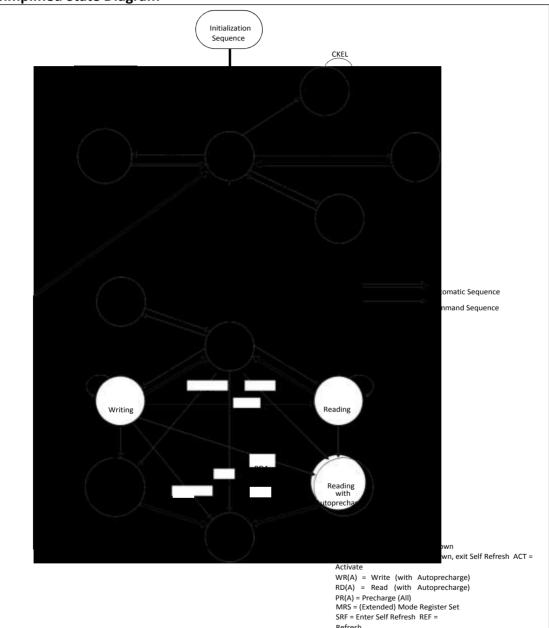

# **Simplified State Diagram**

Note: Use caution with this diagram. It is intended to provide a floor plan of the possible state transitions and the commands to control them, not all details. In particular situations involving more than one bank, enabling/disabling on-die termination, Power Down entry/exit - among other things - are not captured in full detail.

### **Basic Functionality**

Read and write accesses to the DDR2 SDRAM are burst oriented; accesses start at a selected location and continue for a burst length of four or eight in a programmed sequence. Accesses begin with the registration of an Active command, which is then followed by a Read or Write command. The address bits registered coincident with the active command are used to select the bank and row to be accessed (BAO, BA1 select the bank; AO-A13 select the row). The address bits registered coincident with the Read or Write command are used to select the starting column location for the burst access and to determine if the auto precharge command is to be issued.

Prior to normal operation, the DDR2 SDRAM must be initialized. The following sections provide detailed information covering device initialization, register definition, command descriptions and device operation.

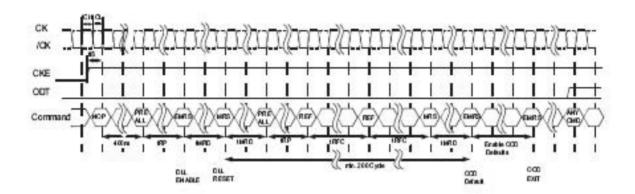

#### Power up and Initialization

DDR2 SDRAMs must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation.

Power-up and Initialization Sequence

The following sequence is required for POWER UP and Initialization.

- 1. Apply power and attempt to maintain CKE below 0.2\*VDDQ and ODT<sup>\*1</sup> at a low state (all other inputs may be undefined.)

- VDD, VDDL and VDDQ are driven from a single power converter output, AND

- VTT is limited to 0.95V max, AND

- Vref tracks VDDQ/2.

or

- Apply VDD before or at the same time as VDDL.

- Apply VDDL before or at the same time as VDDQ.

- Apply VDDQ before or at the same time as VTT & Vref. at

least one of these two sets of conditions must be met.

- 2. Start clock and maintain stable condition.

- 3. For the minimum of 200us after stable power and clock (CK, CK), then apply NOP or deselect & take CKE high.

- 4. Wait minimum of 400ns then issue precharge all command. NOP or deselect applied during 400ns period.

- 5. Issue EMRS(2) command. (To issue EMRS(2) command, provide "Low" to BAO, "High" to BA1.)

- 6. Issue EMRS(3) command. (To issue EMRS(3) command, provide "High" to BAO and BA1.)

- 7. Issue EMRS to enable DLL. (To issue "DLL Enable" command, provide "Low" to A0, "High" to BA0 and "Low" to BA1 and A12.)

- 8. Issue a Mode Register Set command for "DLL reset".

(To issue DLL reset command, provide "High" to A8 and "Low" to BA0-1)

- 9. Issue precharge all command.

- 10. Issue 2 or more auto-refresh commands.

- 11. Issue a mode register set command with low to A8 to initialize device operation. (i.e. to program operating parameters without resetting the DLL.

- 12. At least 200 clocks after step 8, EMRS OCD Default command (A9=A8= A7=1) followed by EMRS OCD Exit command (A9=A8=A7=0) must be issued with other operating parameters of EMRS.

- 13. The DDR2 SDRAM is now ready for normal operation.

\*1) To guarantee ODT off, VREF must be valid and a low level must be applied to the ODT pin.

# Initialization Sequence after Power Up

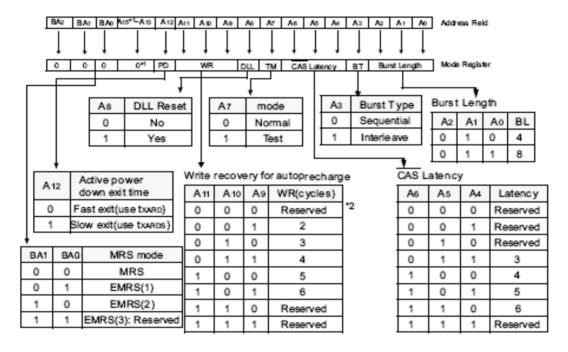

# **Programming the Mode Register**

For application flexibility, burst length, burst type, CAS latency, DLL reset function, write recovery time (tWR) are user defined variables and must be programmed with a Mode Register Set (MRS) command. Additionally, DLL disable function, driver impedance, additive CAS latency, single-ended strobe and ODT (On Die Termination) are also user defined variables and must be programmed with an Extended Mode Register Set (EMRS) command. Contents of the Mode Register (MR) or Extended Mode Registers (EMR(#)) can be altered by re-executing the MRS and EMRS Commands. If the user chooses to modify only a subset of the MRS or EMRS variables, all variables must be redefined when the MRS or EMRS commands are issued.

MRS, EMRS and Reset DLL do not affect array contents, which means initialization including those can be executed any time after power-up without affecting array contents.

### DDR2 SDRAM Mode Register Set (MRS)

The mode register stores the data for controlling the various operating modes of DDR2 SDRAM. It controls CAS latency, burst length, burst sequence, test mode, DLL reset, tWR and various vendor specific options to make DDR2 SDRAM useful for various applications. The default value of the mode register is not defined, therefore the mode register must be written after power-up for proper operation. The mode register is written by asserting low on CS, RAS, CAS, WE, BA0 and BA1, while controlling the state of address pins A0 ~ A13. The DDR2 SDRAM should be in all bank precharge with CKE already high prior to writing into the mode register. The mode register set command cycle time (tMRD) is required to complete the write operation to the mode register. The mode register contents can be changed using the same command and clock cycle requirements during normal operation as long as all banks are in the precharge state. The mode register is divided into various fields depending on functionality. Burst length is defined by A0 ~ A2 with options of 4 and 8 bit burst lengths. The burst length decodes are compatible with DDR SDRAM. Burst address sequence type is defined by A3, CAS latency is defined by A4 ~ A6. The DDR2 doesn't support half clock latency mode. A7 is used for test mode. A8 is used for DLL reset. A7 must be set to low for normal MRS operation. Write recovery time tWR is defined by A9 ~ A11. Refer to the table for specific codes.

<sup>\*1</sup> A14 and A15 is reserved for future usage.

<sup>\*2 :</sup> WR(write recovery for autoprecharge) min is determined by tCK max and WR max is determined by tCK min. WR in clock cycles is calculated by dividing tWR (in ns) by tCK (in ns) and rounding up a non-integer value to the next integer (WR(cycles) = tWR(ns)tCK(ns)). The mode register must be programmed to this value. This is also used with tRP to determine tDAL.

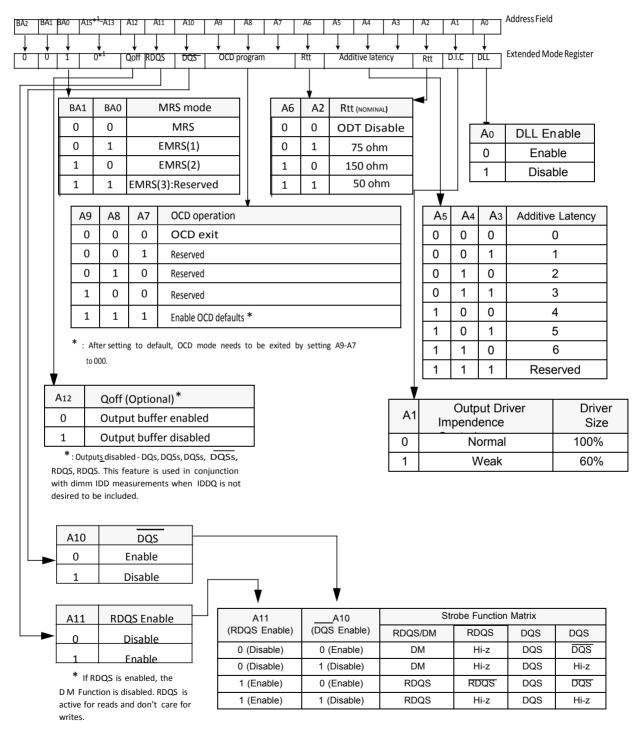

# **DDR2 SDRAM Extended Mode Register Set**

#### EMRS(1)

The extended mode register(1) stores the data for enabling or disabling the DLL, output driver strength, ODT value selection and additive latency. The default value of the extended mode register is not defined, therefore the extended mode register must be written after power-up for proper operation. Extended mode register(1) is written by asserting low on CS, RAS, CAS, WE and high on BA0 and low on BA1, and control-ling rest of pins A0 ~ A13.

The DDR2 SDRAM should be in all bank precharge with CKE already high prior to writing into the extended mode register. The mode register set command cycle time (tMRD) must be satisfied to complete the write operation to the extended mode register. Mode register contents can be changed using the same command and clock cycle requirements during normal operation as long as all banks are in the precharge state. A0 is used for DLL enable or disable. A1 is used for enabling reduced strength data-output drive. A3~A5 determines the additive latency. A2 and A6 are used for ODT value selection, A7~A9 are used for OCD control, A10 is used for DQS disable and A11 is used for RDQS enable.

#### DLL Enable / Disable

The DLL must be enabled for normal operation. DLL enable is required during power up initialization, and upon returning to normal operation after having the DLL disabled. The DLL is automatically disabled when entering self refresh operation and is automatically re-enabled upon exit of self refresh operation. Any time the DLL is enabled (and subsequently reset), 200 clock cycles must occur before a Read command can be issued to allow time for the internal clock to be synchronized with the external clock. Failing to wait for synchronization to occur may result in a violation of the tAC or tDQSCK parameters.

# EMRS(1) Programming

<sup>\*1:</sup> A14 and A15 is reserved for future usage.

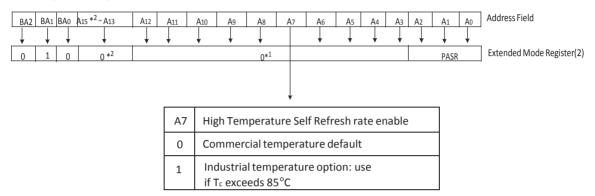

# EMRS(2) Programming\*1: PASR

- \*1: BAO, BA1, and BA2 must be programmed to 0 when setting the mode register during initialization.

- \*2: A14 and A15 is reserved for future usage.

- \*3: While Tc > 85° C, Double refresh rate (tREFI: 3.9us) is required, and to enter self refresh mode at this temperature range it must be required an EMRS command to change itself refresh rate.

The PASR bits allows the user to dynamically customize the memory array size to the actual needs. This feature allows the device to reduce standby current by refreshing only the memory arrays that contain essential data. The refresh options are full array, one-half array, one-quarter array, three-fourth array, or none of the array. The mapping of these partitions can start at either the beginning or the end of the address map. Please see the following table.

| P ASR[2] | P ASR[1] | P ASR[0] | ACTIVE SECTION                |

|----------|----------|----------|-------------------------------|

| 0        | 0        | 0        | Full array                    |

| 0        | 0        | 1        | 1/2 array (Banks 0,1, 2, 3)   |

| 0        | 1        | 0        | 1/4 array (Bank 0, 1)         |

| 0        | 1        | 1        | 1/8 array (Bank 0)            |

| 1        | 0        | 0        | 3/4 array (Banks 2,3,4,5,6,7) |

| 1        | 0        | 1        | 1/2 array (Banks 4, 5, 6, 7)  |

| 1        | 1        | 0        | 1/4 array (Bank 6,7)          |

| 1        | 1        | 1        | 1/8 array (Bank 7)            |

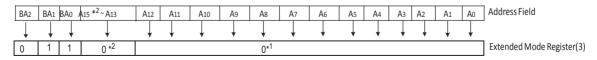

#### EMRS(3) Programming: Reserved\*1

<sup>\*1:</sup>EMRS(3) is reserved for future use and all bits except BA0, BA1, BA2 must be programmed to 0 when setting the mode register during initialization.

<sup>\*2:</sup> A14 and A15 is reserved for future usage.

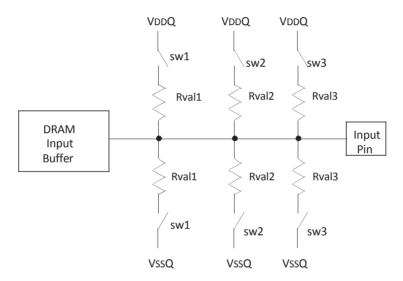

# **On-Die Termination (ODT)**

On Die <u>Termination</u> (O<u>DT) is a feature that allows a DRAM to turn on/off termination resistance for each DQ, UDQS/UDQS, LDQS/LDQS, UDM and LDM via the ODT control pin. The ODT feature is designed to improve signal integrity of the memory channel by allowing the DRAM controller to independently turn on/off termination resistance for any or all DRAM devices.</u>

The ODT function is supported for ACTIVE and STANDBY modes. ODT is turned off and not supported in SELF REFRESH mode.

Switch (sw1, sw2, sw3) is enabled by ODT pin.

Selection among sw1, sw2, and sw3 is determined by "Rtt (nominal)" in EMR. Termination included on all DQs, UDQS/UDQS, LDQS/LDQS, UDM and LDM pins.

# Functional representation of ODT

# **ODT Truth Table**

The ODT Truth Table shows which of the input pins are terminated depending on the state of address bit A10and A11 in the EMRS.

To activate termination of any of these pins, the ODT function has to be enabled in the EMRS by address bits A6 and  $\Delta 2$

| Input Pin   | EMRS<br>Adress Bit A10 | EMRS<br>Adress Bit A11 |

|-------------|------------------------|------------------------|

| DQ0~DQ7     | Х                      | Х                      |

| DQ8~DQ15    | Х                      | Х                      |

| LDQS        | Х                      | Х                      |

| <u>LDQS</u> | 0                      | Х                      |

| UDQS        | Х                      | Х                      |

| UDQS        | 0                      | Х                      |

| LDM         | Х                      | Х                      |

| UDM         | Х                      | Х                      |

X=Don't Care 0=Signal Low 1=Signal High

# DC Electrical Characteristics and Operation Conditions:

| Parameter / Condition                                  | Symbol    | min. | nom. | max. | Units | Notes |

|--------------------------------------------------------|-----------|------|------|------|-------|-------|

| Rtt eff. impedance value for EMRS(A6,A2)= 0,1; 75 ohm  | Rtt1(eff) | 60   | 75   | 90   | ohm   | 1     |

| Rtt eff. impedance value for EMRS(A6,A2)= 1,0; 150 ohm | Rtt2(eff) | 120  | 150  | 180  | ohm   | 1     |

| Rtt eff. impedance value for EMRS(A6,A2)= 1,1; 50 ohm  | Rtt3(eff) | 40   | 50   | 60   | ohm   | 1     |

| Deviation of VM with respect to V <sub>DDQ</sub> /2    | delta VM  | -6   |      | +6   | %     | 2     |

# 1) Measurement Definition for Rtt(eff):

Apply VIHac and VILac to test pin separately, then measure current I(VIHac) and I(VILac) respectively

#### 2) Measurement Definition for VM:

Measure voltage (VM) at test pin (midpoint) with no load:

delta VM = ((

$$2* VM / V_{DDQ}$$

) - 1 ) x 100%

# AC Electrical Characteristics and Operation Conditions:

| Symbol             | Parameter / Condition                | min.                      | max.                                            | Units           | Notes |

|--------------------|--------------------------------------|---------------------------|-------------------------------------------------|-----------------|-------|

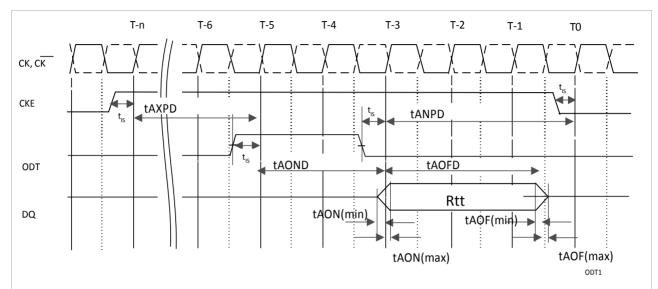

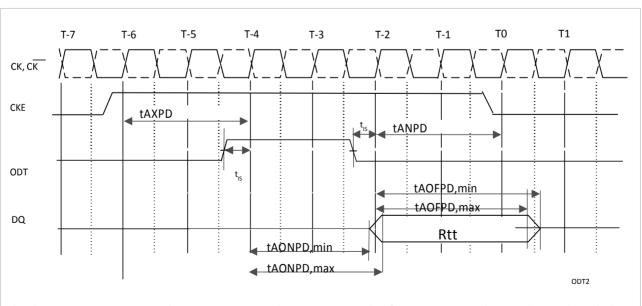

| t <sub>AOND</sub>  | ODT turn-on delay                    | 2                         | 2                                               | t <sub>CK</sub> |       |

| t <sub>AON</sub>   | ODT turn-on                          | t <sub>AC</sub> (min)     | t <sub>AC</sub> (max) + 0.7                     | ns              | 1     |

| t <sub>AONPD</sub> | ODT turn-on (Power-Down Mode)        | t <sub>AC</sub> (min) + 2 | 2 t <sub>CK</sub> + t <sub>AC</sub> (max) + 1   | ns              | 3     |

| t <sub>AOFD</sub>  | ODT turn-off delay                   | 2.5                       | 2.5                                             | t <sub>CK</sub> |       |

| t <sub>AOF</sub>   | ODT turn-off                         | t <sub>AC</sub> (min)     | t <sub>AC</sub> (max) + 0.6                     | ns              | 2     |

| t <sub>AOFPD</sub> | ODT turn-off (Power-Down Mode)       | t <sub>AC</sub> (min) + 2 | 2.5 t <sub>CK</sub> + t <sub>AC</sub> (max) + 1 | ns              | 3     |

| t <sub>ANPD</sub>  | ODT to Power Down Mode Entry Latency | 3                         | х                                               | t <sub>CK</sub> | 4     |

| t <sub>AXPD</sub>  | ODT Power Down Exit Latency          | 8                         |                                                 | t <sub>CK</sub> | 4     |

<sup>1)</sup> ODT turn on time min. is when the device leaves high impedance and ODT resistance begins to turn on. ODT turn on time max. is when the ODT resistance is fully on. Both are measured from t<sub>AOND</sub>.

ODT turn off time min. is when the device stars to turn-off ODT resistance.

ODT turn off time max. is when the bus is in high impedance. Both are measured from t<sub>AOFD</sub>.

<sup>3)</sup> For Standard Active Power-down - with MRS A12 = "0" - the non-power-down timings (  $t_{AOND}$ ,  $t_{AON}$ ,  $t_{AOFD}$  and  $t_{AOF}$  ) apply

<sup>4)</sup> t<sub>ANPD</sub> and t<sub>AXPD</sub> define the timing limit when either Power Down Mode Timings (t<sub>AONPD</sub>, t<sub>AOFPD</sub>) or Non-Power Down Mode timings (t<sub>AOND</sub>, t<sub>AOFD</sub>) have to be applied.

#### ODT Timing for Active / Standby (Idle) Mode and Standard Active Power-Down Mode

- 1) Both ODT to Power Down Entry and Exit Latency timing parameter tANPD and tAXPD are met, therefore Non-Power Down Mode timings have to be applied.

- 2) ODT turn-on time (t<sub>AON,min</sub>) is when the device leaves high impedance and ODT resistance begins to turn on. ODT turn on time max. (t<sub>AON,max</sub>) is when the ODT resistance is fully on. Both are measured from t<sub>AON,D</sub>.

- 3) ODT turn off time min. (t<sub>AOF,min</sub>) is when the device starts to turn off the ODT resistance. ODT turn off time max. (t<sub>AOF,max</sub>) is when the bus is in high impedance. Both are measured from t<sub>AOFD</sub>.

# ODT Timing for Precharge Power-Down and Low Power Power-Down Mode

1) Both ODT to Power Down Entry and Exit Latencies tANPD and tAXPD are not met, therefore Power-Down Mode timings have to be applied.

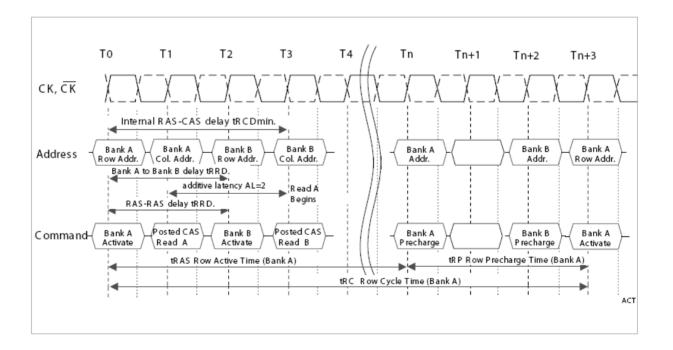

#### **Bank Activate Command**

The Bank Activate command is issued by holding CAS and WE high with CS and RAS low at the rising edge of the clock. The bank addresses of BAO-BA2 are used to select the desired bank. The row addresses AO through A13 are used to determine which row to activate in the selected bank. The Bank Activate command must be applied before any Read or Write operation can be executed. Immediately after the bank active command, the DDR2 SDRAM can accept a read or write command (with or without Auto-Precharge) on the following clock cycle. If an R/W command is issued to a bank that has not satisfied the tRCDmin specification, then additive latency must be programmed into the device to delay the R/W command which is internally issued to the device. The additive latency value must be chosen to assure tRCDmin is satisfied. Additive latencies of 0,1,2,3,4,5 and 6 are supported.

Once a bank has been activated it must be precharged before another Bank Activate command can be applied to the same bank. The bank active and precharge times are defined as tRAS and tRP, respectively. The minimum time interval between successive Bank Activate commands to the same bank is determined (tRC). The minimum time interval between Bank Active commands, to any other bank, is the Bank A to Bank B delay time (tRRD).

Bank Activate Command Cycle: tRCD = 3, AL = 2, tRP = 3, tRRD = 2

#### **Read and Write Commands and Access Modes**

After a bank has been activated, a read or write cycle can be executed. This is accomplished by setting RAS high, CS and CAS low at the clock's rising edge. WE must also be defined at this time to determine whether the access cycle is a read operation (WE high) or a write operation (WE low). The DDR2 SDRAM provides a wide variety of fast access modes. The boundary of the burst cycle is restricted to specific segments of the page length.

For example, the 16Mbit x 16 I/O x 8 Bank chip has a page length of 1024 bits ( defined by CA0-CA9 ). In case of a 4-bit burst operation ( burst length = 4 ) the page length of 1024 bits is divided into 256 uniquely addressable segments ( 4-bits x 16 I/O each ). The 4-bit burst operation will occur entirely within one of the 256 segments ( defined by CA0-CA7 ) beginning with the column address supplied to the device during the Read or Write Command ( CA0-CA9 ). The second, third and fourth access will also occur within this segment, however, the burst order is a function of the starting address, and the burst sequence.

In case of an 8-bit burst operation ( burst length = 8 ) the page length of 1024 bits is divided into 128 uniquely addressable double segments ( 8-bits x 16 I/O each ). The 8-bit burst operation will occur entirely within one of the 128 double segments ( defined by CAO-CA6 ) beginning with the column address supplied to the deivce during the Read or Write Command ( CAO-CA9 ).

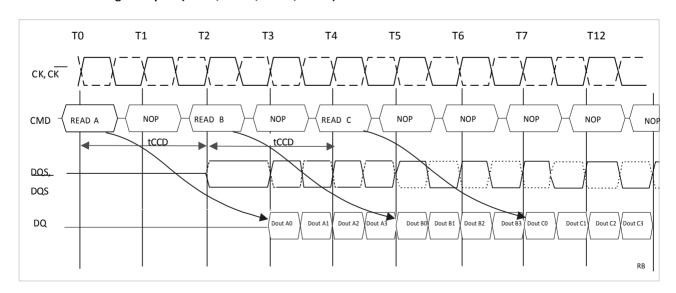

A new burst a<u>ccess must</u> not interrupt the previous 4 bit burst operation in case of BL = 4 setting. Therefore the minimum CAS to CAS delay (tCCD) is a minimum of 2 clocks for read or write cycles.

For 8 bit burst operation (BL = 8) the minimum CAS to CAS delay (tCCD) is 4 clocks for read or write cycles. Burst interruption is allowed with 8 bit burst operation. For details see the "Burst Interrupt" - Section of this datasheet.

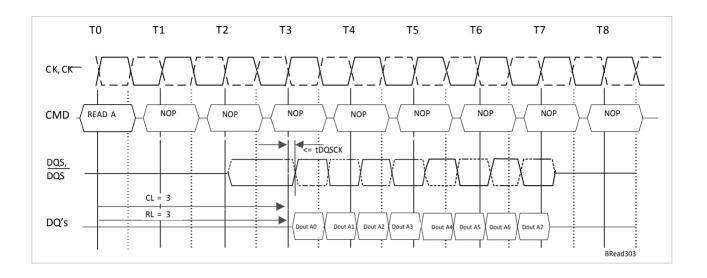

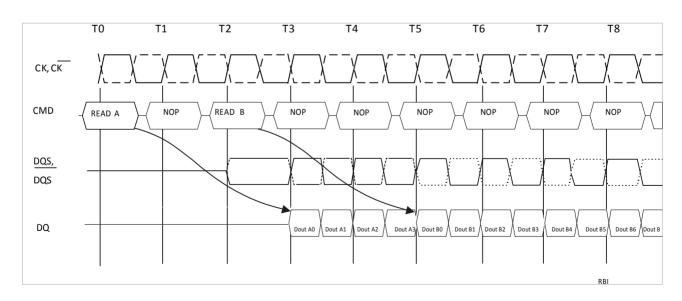

#### Read Burst Timing Example: (CL = 3, AL = 0, RL = 3, BL = 4)

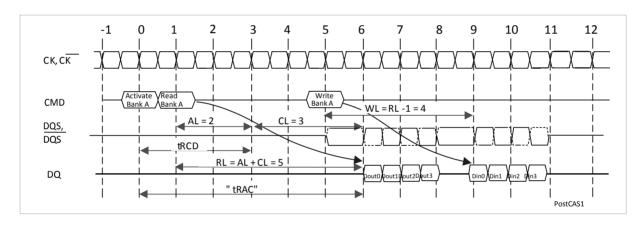

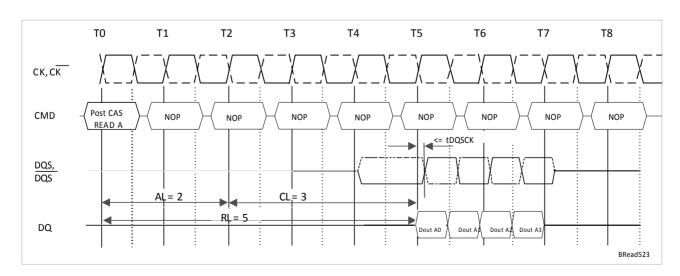

# Posted CAS

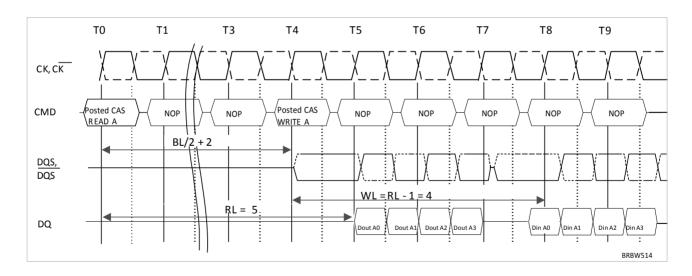

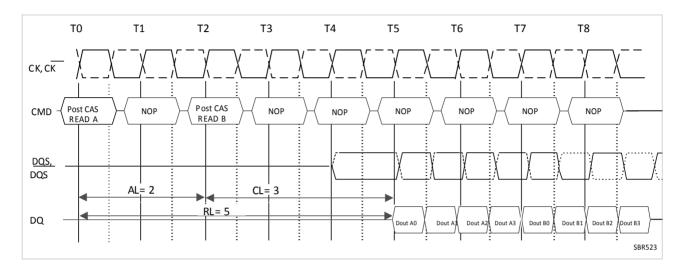

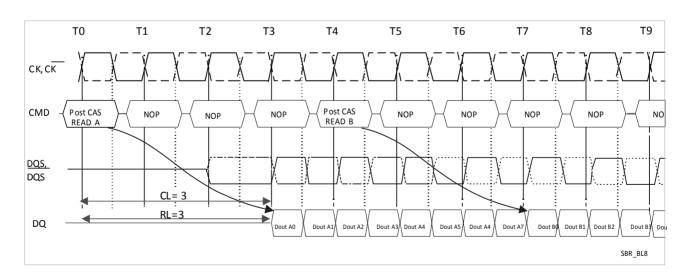

Posted  $\overline{\text{CAS}}$  operation is supported to make command and data bus efficient for sustainable bandwidths in DDR2 SDRAM. In this operation, the DDR2 SDRAM allows a Read or Write command to be issued immediately after the  $\overline{\text{RAS}}$  bank activate command (or any time during the  $\overline{\text{RAS}}$  to  $\overline{\text{CAS}}$  delay time, tRCD, period). The command is held for the time of the Additive Latency (AL) before it is issued inside the device. The Read Latency (RL) is the sum of AL and the  $\overline{\text{CAS}}$  latency (CL). Therefore if a user chooses to issue a Read/Write command before the tRCDmin, then AL greater than 0 must be written into the EMRS. The Write Latency (WL) is always defined as RL - 1 (Read Latency -1) where Read Latency is defined as the sum of Additive Latency plus  $\overline{\text{CAS}}$  latency (RL=AL+CL). If a user chooses to issue a Read command after the tRCDmin period, the Read Latency is also defined as RL = AL + CL.

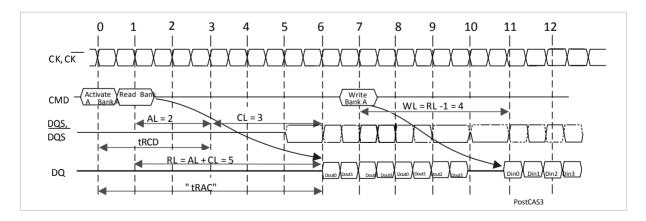

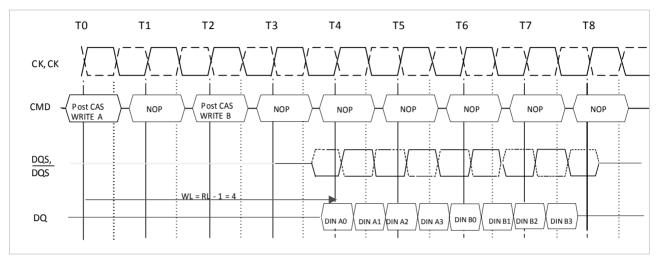

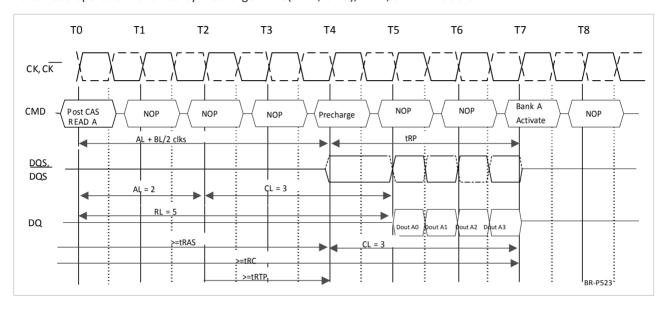

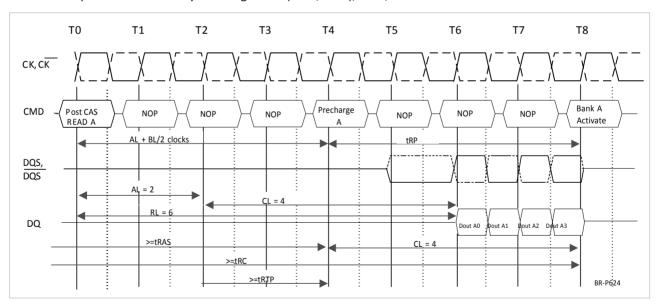

Read followed by a write to the same bank, Activate to Read delay < tRCDmin: AL = 2 and CL = 3, RL = (AL + CL) = 5, WL = (RL - 1) = 4, BL = 4

Read followed by a write to the same bank, Activate to Read delay < tRCDmin: AL = 2 and CL = 3, RL = (AL + CL) = 5, WL = (RL - 1) = 4, BL = 8

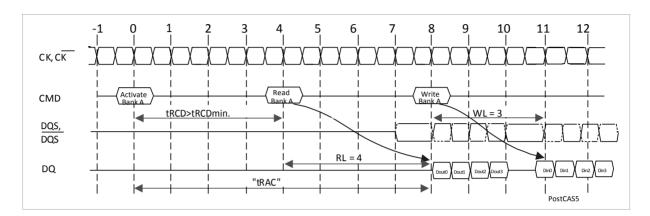

Read followed by a write to the same bank, Activate to Read delay > tRCDmin: AL = 1, CL = 3, RL = 4, WL = 3, BL = 4

# **Burst Mode Operation**

Burst mode operation is used to provide a constant flow of data to memory locations (write cycle), or from memory locations (read cycle). The parameters that define how the burst mode will operate are burst sequence and burst length.

The DDR2 SDRAM supports 4 bit and 8 bit burst modes only. For 8 bit burst mode, full interleave address ordering is supported, however, sequential address ordering is nibble based for ease of implementation. The burst length is programmable and defined by the addresses A0 ~ A2 of the MRS. The burst type, either sequential or interleaved, is programmable and defined by the address bit 3 (A3) of the MRS. Seamless burst read or write operations are supported.

Interruption of a burst read or write operation is prohibited, when burst length = 4 is programmed. For burst interruption of a read or write burst when burst length = 8 is used, see the "Burst Interruption" section of this datasheet. A Burst Stop command is not supported on DDR2 SDRAM devices.

#### **Burst Length and Sequence**

| Burst Length | Starting Address (<br>A2 A1 A0 ) | Sequential Addressing (decimal) | Interleave Addressing (decimal) |

|--------------|----------------------------------|---------------------------------|---------------------------------|

|              | x 0 0                            | 0, 1, 2, 3                      | 0, 1, 2, 3                      |

| 4            | x 0 1                            | 1, 2, 3, 0                      | 1, 0, 3, 2                      |

| 4            | x 1 0                            | 2, 3, 0, 1                      | 2, 3, 0, 1                      |

|              | x 1 1                            | 3, 0, 1, 2                      | 3, 2, 1, 0                      |

|              | 000                              | 0, 1, 2, 3, 4, 5, 6, 7          | 0, 1, 2, 3, 4, 5, 6, 7          |

|              | 001                              | 1, 2, 3, 0, 5, 6, 7, 4          | 1, 0, 3, 2, 5, 4, 7, 6          |

|              | 010                              | 2, 3, 0, 1, 6, 7, 4, 5          | 2, 3, 0, 1, 6, 7, 4, 5          |

| 8            | 011                              | 3, 0, 1, 2, 7, 4, 5, 6          | 3, 2, 1, 0, 7, 6, 5, 4          |

| 8            | 100                              | 4, 5, 6, 7, 0, 1, 2, 3          | 4, 5, 6, 7, 0, 1, 2, 3          |

|              | 101                              | 5, 6, 7, 4, 1, 2, 3, 0          | 5, 4, 7, 6, 1, 0, 3, 2          |

|              | 110                              | 6, 7, 4, 5, 2, 3, 0, 1          | 6, 7, 4, 5, 2, 3, 0, 1          |

|              | 111                              | 7, 4, 5, 6, 3, 0, 1, 2          | 7, 6, 5, 4, 3, 2, 1, 0          |

Note: 1) Page length is a function of I/O organization and column addressing.

2) Order of burst access for sequential addressing is "nibble-based" and therefore different from SDR or DDR components.

#### **Burst Read Command**

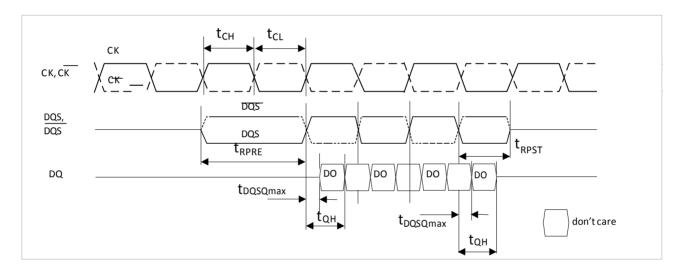

The Burst Read command is initiated by having CS and CAS low while holding RAS and WE high at the rising edge of the clock. The address inputs determine the starting column address for the burst. The delay from the start of the command until the data from the first cell appears on the outputs is equal to the value of the read latency (RL). The data strobe output (DQS) is driven low one clock cycle before valid data (DQ) is driven onto the data bus. The first bit of the burst is synchronized with the rising edge of the data strobe (DQS). Each subsequent data-out appears on the DQ pin in phase with the DQS signal in a source synchronous manner. The RL is equal to an additive latency (AL) plus CAS latency (CL). The CL is defined by the Mode Register Set (MRS). The AL is defined by the Extended Mode Register Set (EMRS).

#### **Basic Burst Read Timing**

# Burst Read Operation: RL = 5 (AL = 2, CL = 3, BL = 4)

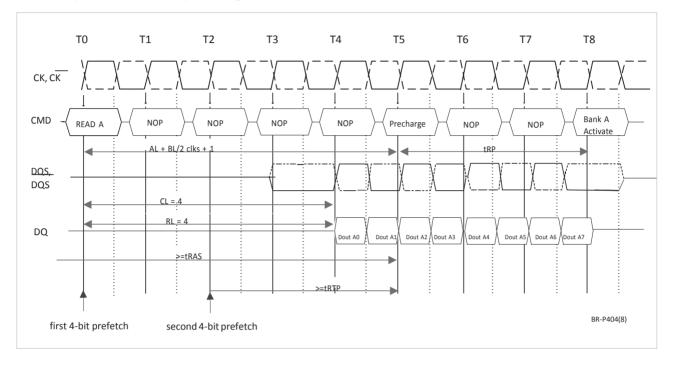

Burst Read Operation: RL = 3 (AL = 0, CL = 3, BL = 8)

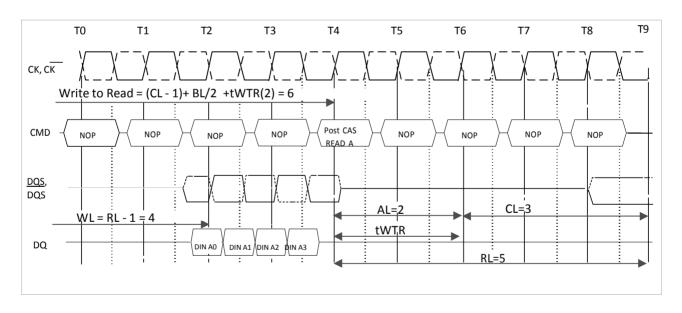

Bust Read followed by Bust Write: RL = 5, WL = (RL-1) = 4, BL = 4

The minimum time from the burst read command to the burst write command is defined by a read-to-write turn-around time, which is BL/2 + 2 clocks.

Seamless Burst Read Operation: RL = 5, AL = 2, CL = 3, BL = 4

The seamless burst read operation is supported by enabling a read command at every BL / 2 number of clocks. This operation is allowed regardless of same or different banks as long as the banks are activated.

# Seamless Burst Read Operation: RL = 3, AL = 0, CL = 3, BL = 8 (non-interrupting)

The seamless, non-interrupting 8-bit burst read operation is supported by enabling a read command at every BL / 2 number of clocks. This operation is allowed regardless of same or different banks as long as the banks are activated.

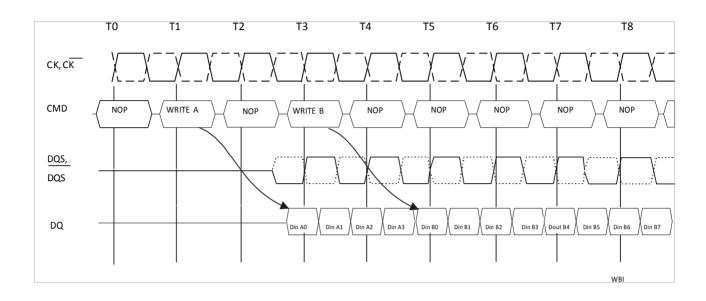

#### **Burst Write Command**

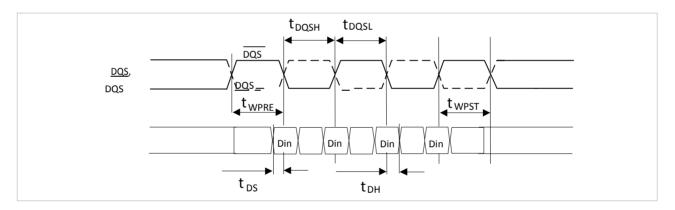

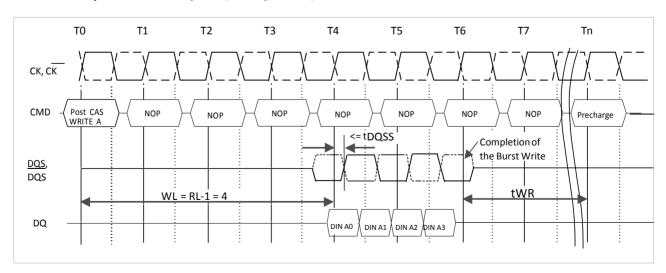

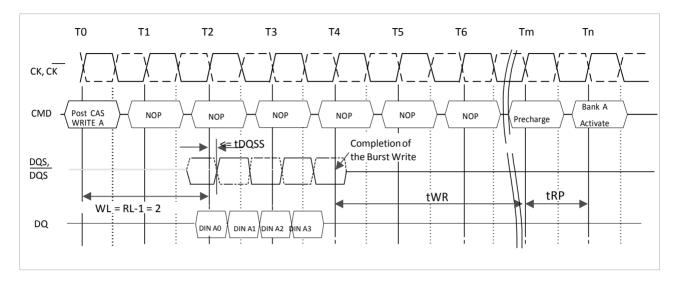

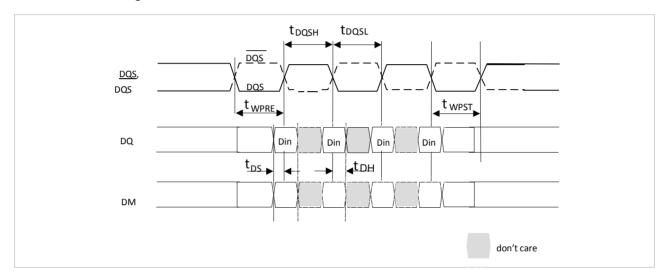

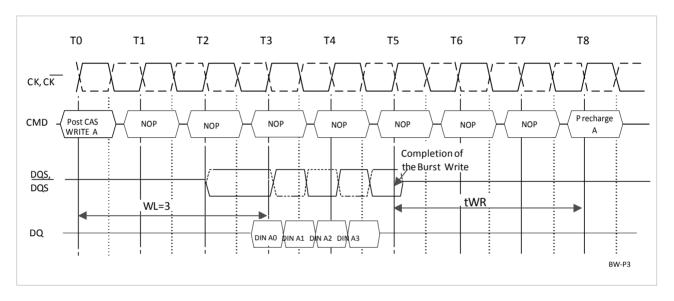

The Burst Write command is initiated by having CS, CAS and WE low while holding RAS high at the rising edge of the clock. The address inputs determine the starting column address. Write latency (WL) is defined by a read latency (RL) minus one and is equal to (AL + CL -1). A data strobe signal (DQS) should be driven low (preamble) one clock prior to the WL. The first data bit of the burst cycle must be applied to the DQ pins at the first rising edge of the DQS following the preamble. The tDQSS specification must be satisfied for write cycles. The subsequent burst bit data are issued on successive edges of the DQS until the burst length is completed. When the burst has finished, any additional data supplied to the DQ pins will be ignored. The DQ signal is ignored after the burst write operation is complete. The time from the completion of the burst write to bank precharge is named "write recovery time" (tWR) and is the time needed to store the write data into the memory array. tWR is an analog timing parameter (see the AC table in this specification) and is not the programmed value for WR in the MRS.

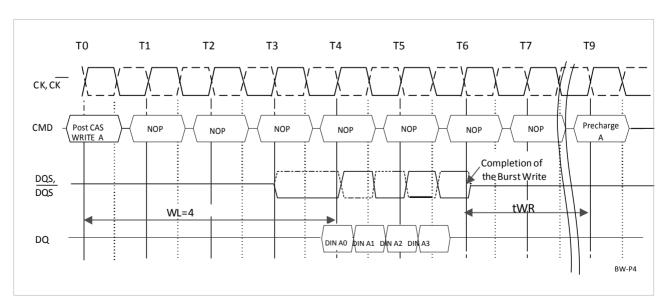

#### **Basic Burst Write Timing**

Burst Write Operation: RL = 5 (AL = 2, CL = 3), WL = 4, BL = 4

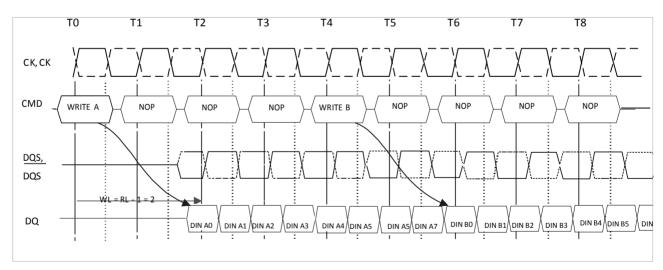

#### Burst Write Operation: RL = 3 (AL = 0, CL = 3), WL = 2, BL = 4

# Burst Write followed by Burst Read: RL = 5 (AL = 2, CL = 3), WL = 4, tWTR = 2, BL = 4

The minimum number of clocks from the burst write command to the burst read command is

(CL-1)+BL/2+tWTR

where tWTR is the write-to-read turn-around time tWTR expressed in clock cycles. The tWTR is not a write recovery time (tWR) but the time required to transfer 4 bit write data from the input buffer into sense amplifiers in the array.

Seamless Burst Write Operation: RL=5, WL=4, BL=4

The seamless burst write operation is supported by enabling a write command every BL/2 number of clocks. This operation is allowed regardless of same or different banks as long as the banks are activated.

Seamless Burst Write Operation: RL=3, WL=2, BL=8, non-interrupting

The seamless, non-interrupting 8-bit burst write operation is supported by enabling a write command at every BL / 2 number of clocks. This operation is allowed regardless of same or different banks as long as the banks are activated.

#### Write Data Mask

Two write data mask inputs (LDM, UDM) are supported on x16 components of DDR2 SDRAMs, consistent with the implementation on DDR SDRAMs. It has identical timings on write operations as the data bits, and though used in a uni-directional manner, is internally loaded identically to data bits to insure matched system timing. Data mask is not used during read cycles. If DM is high during a write burst coincident with the write data, the write data bit is not written to the memory.

# Write Data Mask Timing

Burst Write Operation with Data Mask: RL = 3 (AL = 0, CL = 3), WL = 2, tWR = 3, BL = 4

# **Burst Interruption**

Interruption of a read or write burst is prohibited for burst length of 4 and only allowed for burst length of 8 under the following conditions:

- 1. A Read Burst of 8 can only be interrupted by another Read command. Read burst interruption by a Write or Precharge Command is prohibited.

- 2. A Write Burst of 8 can only be interrupted by another Write command. Write burst interruption by a Read or Precharge Command is prohibited.

- 3. Read burst interrupt must occur exactly two clocks after the previous Read command. Any other Read burst interrupt timings are prohibited.

- 4. Write burst interrupt must occur exactly two clocks after the previous Write command. Any other Read burst interrupt timings are prohibited.

- 5. Read or Write burst interruption is allowed to any bank inside the DDR2 SDRAM.

- 6. Read or Write burst with Auto-Precharge enabled is not allowed to be interrupted.

- 7. Read burst interruption is allowed by a Read with Auto-Precharge command.

- 8. Write burst interruption is allowed by a Write with Auto-Precharge command.

- 9. All command timings are referenced to burst length set in the mode register. They are not referenced to the actual burst. For example, Minimum Read to Precharge timing is AL + BL/2 where BL is the burst length set in the mode register and not the actual burst (which is shorter because of interrupt). Minimum Write to Precharge timing is WL + BL/2

- + tWR, where tWR starts with the rising clock after the un-interrupted burst end and not form the end of the actual burst end.

### Read Burst Interrupt Timing Example: (CL = 3, AL = 0, RL = 3, BL = 8)

Write Bburst Interrupt Timing Example: (CL = 3, AL = 0, WL = 2, BL = 8)

# **Precharge Command**

The Precharge Command is used to precharge or close a bank that has been activated. The Precharge Command is triggered when CS, RAS and WE are low and CAS is high at the rising edge of the clock. The Pre-charge Command can be used to precharge each bank independently or all banks simultaneously. Four address bits A10, BA2, BA1 and BA0 are used to define which bank to precharge when the command is issued.

#### **Bank Selection for Precharge by Address Bits**

| A10 | BA0  | BA1  | BA2  | Precharge<br>Bank(s) |

|-----|------|------|------|----------------------|

| LOW | LOW  | LOW  | LOW  | Bank 0 only          |

| LOW | HIGH | LOW  | LOW  | Bank 1 only          |

| LOW | LOW  | HIGH | LOW  | Bank 2 only          |

| LOW | HIGH | HIGH | LOW  | Bank 3 only          |

| LOW | LOW  | LOW  | HIGH | Bank 4 only          |

| A10  | BA0        | BA1        | BA2        | Precharge<br>Bank(s) |

|------|------------|------------|------------|----------------------|

| LOW  | HIGH       | LOW        | HIGH       | Bank 5 only          |

| LOW  | LOW        | HIGH       | HIGH       | Bank 6 only          |

| LOW  | HIGH       | HIGH       | HIGH       | Bank 7 only          |

| HIGH | Don't Care | Don't Care | Don't Care | All Banks            |

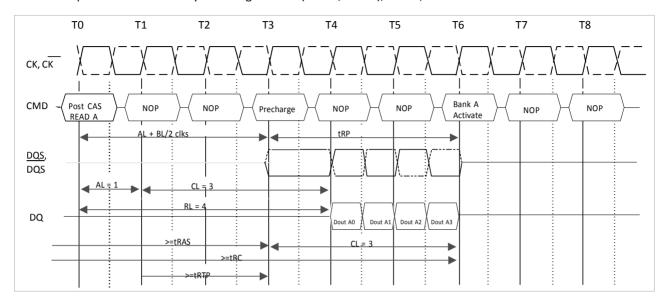

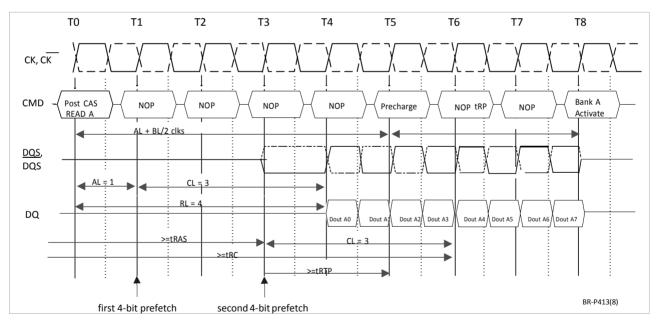

#### **Burst Read Operation Followed by a Precharge**

The following rules apply as long as the tRTP timing parameter - Internal Read to Precharge Command delay time - is less or equal two clocks, which is the case for operating frequencies less or equal 266 MHz (DDR2 400 and 533 speed sorts):

Minimum Read to Precharge command spacing to the same bank = AL + BL/2 clocks. For the earliest possible precharge, the precharge command may be issued on the rising edge which is "Additive Latency (AL) + BL/2 clocks" after a Read Command, as long as the minimum tRAS timing is satisfied.

A new bank active command may be issued to the same bank if the following two conditions are satisfied simultaneously:

- (1) The RAS precharge time (tRP) has been satisfied from the clock at which the precharge begins.

- (2) The RAS cycle time (tRCmin) from the previous bank activation has been satisfied.

For operating frequencies higher than 266 MHz, tRTP becomes > 2 clocks and one additional clock cycle has to be added for the minimum Read to Precharge command spacing, which now becomes AL + BL/2 + 1 clocks.

Burst Read Operation Followed by Precharge: RL = 4 (AL = 1, CL = 3), BL = 4, tRTP <= 2 clocks

Burt Read Operation Followed by Precharge: RL = 4 (AL = 1, CL = 3), BL = 8, tRTP <= 2 clocks

Burst Read operation Followed by Precharge: RL=5(AL=2, CL=3), BL=4, tRTP<=2 clocks

Burst Read operation Followed by Precharge: RL=6(AL=2, CL=4), BL=4, tRTP<=2 clocks

Burst Read Operation Followed by Precharge: RL=4, (AL=0, CL=4), BL=8, tRTP>2 clocks

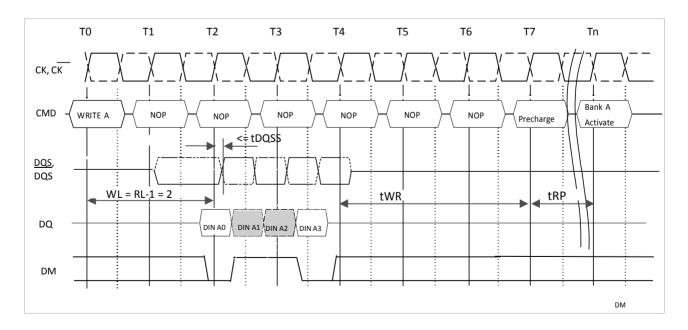

### **Burst Write followed by Precharge**

Minimum Write to Precharge command spacing to the same bank = WL + BL/2 + tWR. For write cycles, a delay must be satisfied from the completion of the last burst write cycle until the Precharge command can be issued. This delay is known as a write recovery time (t WR) referenced from the completion of the burst write to the Precharge command. No Precharge command should be issued prior to the tWR delay, as DDR2 SDRAM does not support any burst interrupt by a Precharge command. tWR is an analog timing parameter (see the AC table in this datasheet) and is not the programmed value for tWR in the MRS.

#### Burst Write followed by Precharge: WL = (RL - 1) = 3, BL = 4, tWR = 3

Burst Write followed by Precharge: WL = (RL - 1) = 4, BL = 4, tWR = 3

# **Auto-Precharge Operation**

Before a new row in an active bank can be opened, the active bank mustt be precharged using either the Precharge Command or the Auto-Precharge function. When a Read or a Write Command is given to the DDR2 SDRAM, the CAS timing accepts one extra address, column address A10, to allow the active bank to automatically begin precharge at the earliest possible moment during the burst read or write cycle. If A10 is low when the Read or Write Command is issued, then normal Read or Write burst operation is executed and the bank remains active at the completion of the burst sequence. If A10 is high when the Read or Write Command is issued, then the Auto-Precharge function is enabled. During Auto-Precharge, a Read Command will execute as normal with the exception that the active bank will begin to precharge internally on the rising edge which is CAS Latency (CL) clock cycles before the end of the read burst. Auto-Precharge is also implemented for Write Commands. The precharge operation engaged by the Auto-Precharge command will not begin until the last data of the write burst sequence is properly stored in the memory array. This feature allows the pre- charge operation to be partially or completely hidden during burst read cycles (dependent upon CAS Latency) thus improving system performance for random data access. The RAS lockout circuit internally delays the Precharge operation until the array restore operation has been completed so that the Auto-Precharge command may be issued with any read or write command.

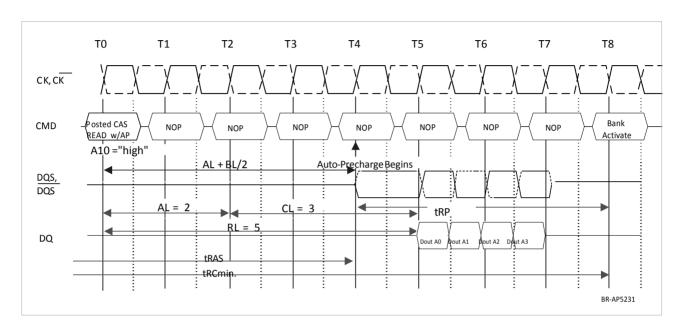

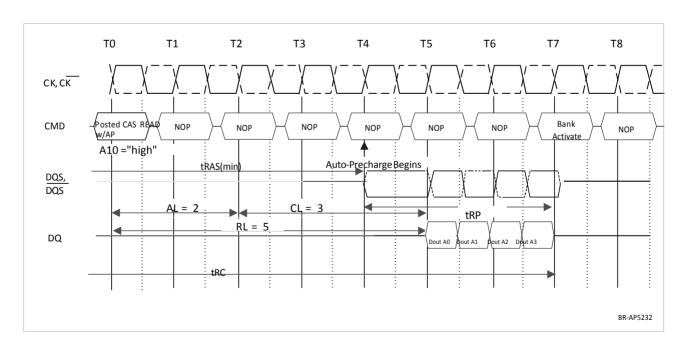

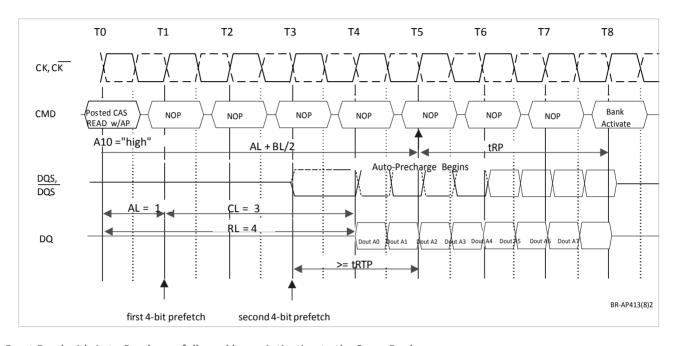

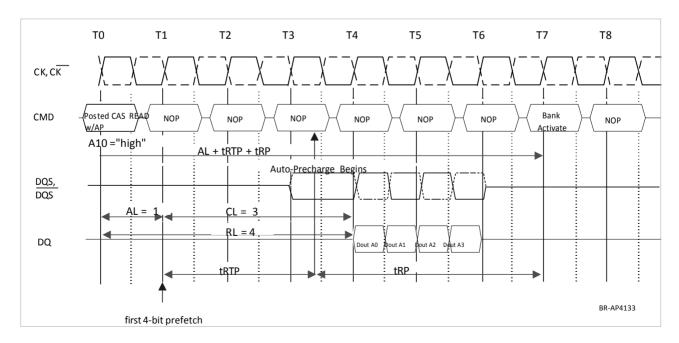

#### Burst Read with Auto-Precharge

If A10 is high when a Read Command is issued, the Read with Auto-Precharge function is engaged. The DDR2 SDRAM starts an Auto-Precharge operation on the rising edge which is (AL + BL/2) cycles later from the Read with AP command if tRAS(min) and tRTP are satisfied. If tRAS(min) is not satisfied at the edge, the start point of Auto-Precharge operation will be delayed until tRAS(min) is satisfied. If tRTP(min) is not satisfied at the edge, the start point of Auto-precharge operation will be delayed until tRTP(min) is satisfied.

In case the internal precharge is pushed out by tRTP, tRP starts at the point where the internal precharge happens (not at the next rising clock edge after this event). So for BL = 4 the minimum time from Read with Auto-Precharge to the next Activate command becomes AL + tRTP + tRP. For BL = 8 the time from Read with Auto-Precharge to the next Activate command is AL + 2 + tRTP + tRP. Note thatt both parameters tRTP and tRP have to be rounded up to the next integer value. In any event internal precharge does not start earlier than two clocks after the last t 4-bit prefetch.

A new bank active (command) may be issued to the same bank if the following two conditions are satisfied simultaneously:

- (1) The RAS precharge time (tRP) has been satisfied from the clock at which the Auto-Precharge begins.

- (2) The RAS cycle time (tRC) from the previous bank activation has been satisfied.

Burst Read with Auto-Precharge followed by an activation to the Same Bank (tRC Limit) RL = 5 (AL = 2,

Burst Read with Auto-Precharge followed by an Activation to the Same Bank (tRAS Limit): RL = 5 (AL

Burst Read with Auto-Precharge followed by an Activation to the Same Bank: RL=4(AL=1,

# CL=3), BL=8, tRTP<=2 clocks

Burst Read with Auto-Precharge followed by an Activation to the Same Bank:

RL=4(AL=1, CL=3), BL=4, tRTP>2 clocks

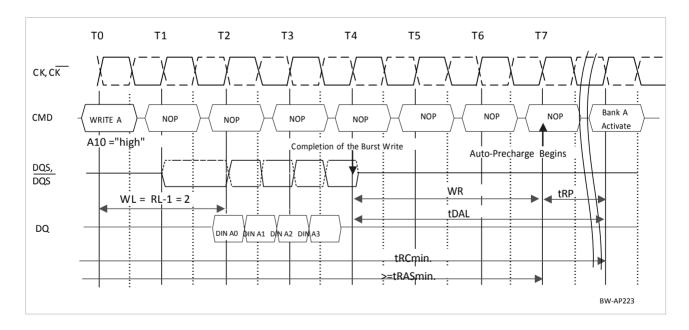

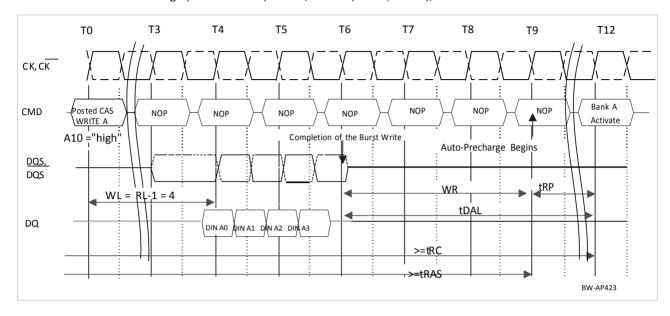

### Burst Write with Auto-Precharge

If A10 is high when a Write Command is issued, the Write with Auto-Precharge function is engaged. The DDR2 SDRAM automatically begins precharge operation after the completion of the write burst plus the write recovery time delay (WR), programmed in the MRS register, as long as tRAS is satisfied. The bank undergoing Auto-Precharge from the completion of the write burst may be reactivated if the following two conditions are satisfied.

- (1) The last data-in to bank activate delay time (tDAL = WR + tRP) has been satisfied.

- (2) The RAS cycle time (tRC) from the previous bank activation has been satisfied.

In DDR2 SDRAMs the write recovery time delay (WR) has to be programmed into the MRS mode register. As long as the analog tWR timing parameter is not violated, WR can be programmed between 2 and 6 clock cycles. Minimum Write to Activate command spacing to the same bank = WL + BL/2 + tDAL.

#### E xamples:

Burst Write with Auto-Precharge (tRC Limit): WL = 2, tDAL = 6 (WR = 3, tRP = 3), BL = 4

Burst Write with Auto-Precharge (WR+tRP Limit): WL=4, tDAL=6(WR=3, tRP=3), BL=4

## **Concurrent Auto-Precharge**

DDR2 devices support the "concurrent Auto-Precharge" feature. A read with Auto-Precharge enabled, or a write with Auto-Precharge enabled, may be followed by any command to the other bank, as long as that command does not interrupt the read or write data transfer, and all other related limitations (e.g. contention between Read data and Write data must be avoided externally and on the internal data bus.

The minimum delay from a read or write command with Auto-Precharge enabled, to a command to a different bank, is summarized in the table below. As defined, the WL = RL - 1 for DDR2 devices which allows the command gap and corresponding data gaps to be minimized.

| FromCommand | To Command<br>(differentbank,<br>non-interrupting command) | Minimum Delay with<br>Concurrent Auto-Pre-<br>charge Suppot | Units |

|-------------|------------------------------------------------------------|-------------------------------------------------------------|-------|

|             | Read or Read w/AP                                          | (CL -1) + (BL/2) + tWTR                                     | tCK   |

| WRITE w/AP  | Write or Write w/AP                                        | BL/2                                                        | tCK   |

|             | Precharge or Activate                                      | 1                                                           | tCK   |

|             | Read or Read w/AP                                          | BL/2                                                        | tCK   |

| Read w/AP   | Write or Write w/AP                                        | BL/2 + 2                                                    | tCK   |

|             | Precharge or Activate                                      | 1                                                           | tCK   |

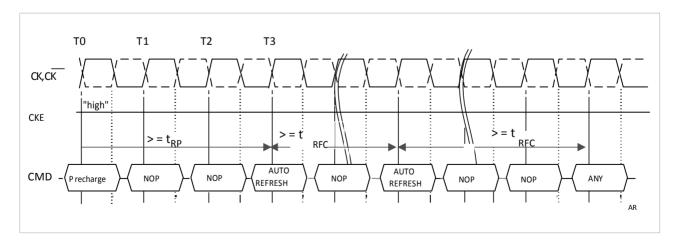

### Refresh

SDRAMs require a refresh of all rows in any rolling 64 ms interval. Each refresh is generated in one of two ways: by an explicit Auto-Refresh command, or by an internally timed event in Self-Refresh mode. Dividing the number of device rows into the rolling 64 ms interval defined the average refresh interval tREFI, which is a guideline to controllers for distributed refresh timing. For example, a 512Mbit DDR2 SDRAM has 8192 rows resulting in a tREFI of 7,8 µs.

### **Auto-Refresh Command**

Auto-Refresh is used during normal operation of the DDR2 SDRAMs. This command is non-persistent, so it must be issued each time a refresh is required. The refresh addressing is generated by the internal refresh controller. This makes the address bits "Don't Care" during an Auto-Refresh command. The DDR2 SDRAM requires Auto-Refresh cycles at an average periodic interval of tREFI (maximum).

When CS, RAS and CAS are held low and WE high at the rising edge of the clock, the chip enters the Auto- Refresh mode. All banks of the SDRAM must be precharged and idle for a minimum of the Precharge time (t<sub>RP</sub>) before the Auto-Refresh Command can be applied. An internal address counter supplies the addresses during the refresh cycle. No control of the external address bus is required once this cycle has started.

When the refresh cycle has completed, all banks of the SDRAM will be in the precharged (idle) state. A delay between the Auto-Refresh Command and the next Activate Command or subsequent Auto-Refresh Command must be greater than or equal to the Auto-Refresh cycle time (t<sub>RFC</sub>).

To allow for improved efficiency in scheduling and switching between tasks, some flexibility in the absolute refresh interval is provided. A maximum of eight Auto-Refresh commands can be posted to any given DDR2 SDRAM, meaning that the maximum absolute interval between any Auto-Refresh command and the next Auto-Refresh command is 9 \* tREFI.

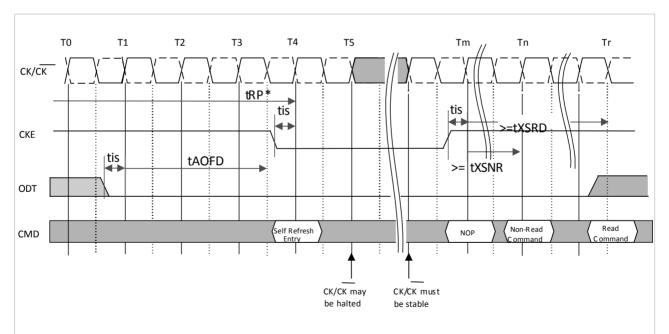

## Self-Refresh Command

The Self-Refresh command can be used to retain data, even if the rest of the system is powered down. When in the Self-Refresh mode, the DDR2 SDRAM retains data without external clocking.

The DDR2 SDRAM device has a built-in timer to accommodate Self-Refresh operation. The Self-Refresh Command is defined by having CS, RAS, CAS and CKE held low with WE high at the rising edge of the clock. ODT must be turned off before issuing Self Refresh command, by either driving ODT pin low or using EMRS command. Once the command is registered, CKE must be held low to keep the device in Self- Refresh mode. When the DDR2 SDRAM has entered Self-Refresh mode, all of the external control signals, except CKE, are disabled. The clock is internally disabled during Self-Refresh Operation to save power. The user may change the external clock frequency or halt the external clock one clock after Self-Refresh entry is registered, how-ever, the clock must be restarted and stable before the device can exit Self-Refresh operation.

Once Self-Refresh Exit command is registered, a delay equal or longer than the tXSNR or tXSRD must be satisfied before a valid command can be issued to the device. CKE must remain high for the entire Self- Refresh exit period (tXSNR or tXSRD) for proper operation. NOP or DESELECT commands must be registered on each positive clock edge during the Self-Refresh exit interval. Since the ODT function is not sup- ported during Self-Refresh operation, ODT has to be turned off before entering Self-Refresh Mode (tAOFD) and can be turned on again when the tXSRD timing is satisfied.

\* = Device must be in the "All banks idle" state to entering Self Refresh mode. ODT must be turned off prior to entering Self Refresh mode.

${\it tXSRD}\ has\ to\ be\ satisfied\ for\ a\ Read\ or\ a\ Read\ with\ Auto-Precharge\ command.$

tXSNR has to be satisfied for any command except a Read or a Read with Auto-Precharge command.

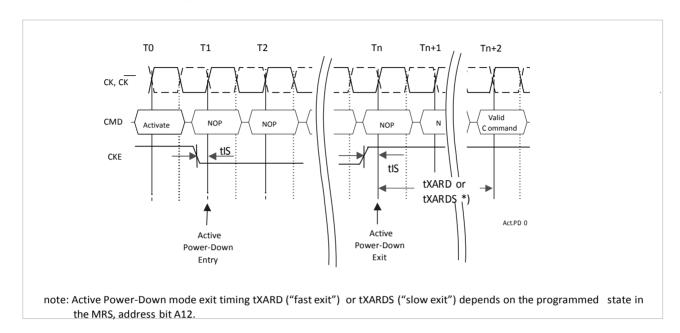

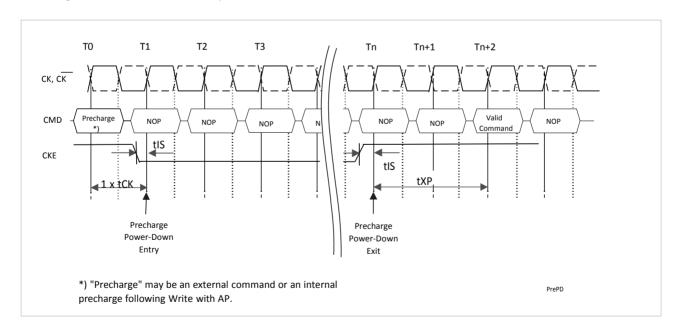

#### Power-Down

Power-down is synchronously entered when CKE is registered low along with NOP or Deselect command. No read or write operation may be in progress when CKE goes low. These operations are any of the following: read burst or write burst and recovery. CKE is allowed to go low while any of other operations such as row activation, precharge or autoprecharge, mode register or extended mode register command time, or auto refresh is in progress. The DLL should be in a locked state when power-down is entered. Otherwise DLL should be reset after exiting power-down mode for proper read operation.

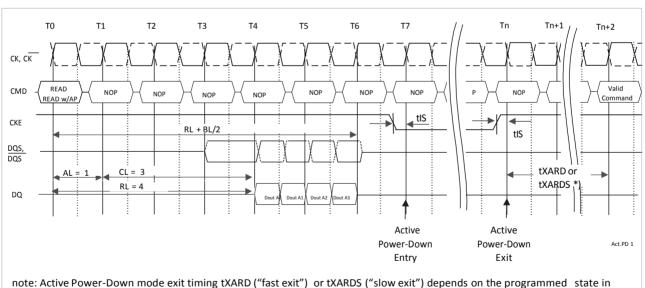

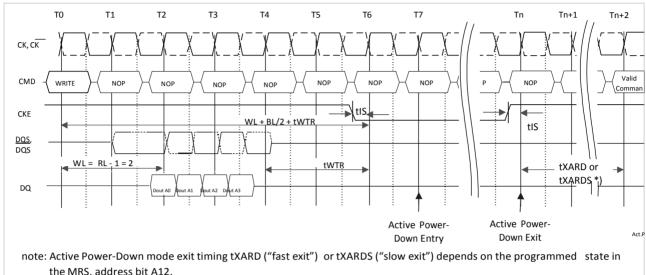

If power-down occurs when all banks are precharged, this mode is referred to as *Precharge Power-down*; if power-down occurs when there is a row active in any bank, this mode is referred to as *Active Power-down*. For *Active Power-down* two different power saving modes can be selected within the MRS register, address bit A12. When A12 is set to "low" this mode is referred as "standard active power-down mode" and a fast power-down exit timing defined by the tXARD timing parameter can be used. When A12 is set to "high" this mode is referred as a power saving "low power active power-down mode". This mode takes longer to exit from the power-down mode and the tXARDS timing parameter has to be satisfied.

Entering power-down deactivates the input and output buffers, excluding CK, CK, ODT and CKE. Also the DLL is disabled upon entering precharge power-down or slow exit active power-down, but the DLL is kept enabled during fast exit active power-down. In power-down mode, CKE low and a stable clock signal must be maintained at the inputs of the DDR2 SDRAM, and all other input signals are "Don't Care". Power-down duration is limited by 9 times tREFI of the device.

The power-down state is synchronously exited when CKE is registered high (along with a NOP or Deselect command). A valid, executable command can be applied with power-down exit latency, tsp., tXARD or tXARDS, after CKE goes high. Power-down exit latencies are defined in the AC spec table of this data sheet.

### Power-Down Entry

Active Power-down mode can be entered after an activate command. Precharge Power-down mode can be entered after a precharge, precharge-all or internal precharge command. It is also allowed to enter power- mode after an Auto-Refresh command or MRS / EMRS command when timed is satisfied.

Active Power-down mode entry is prohibited as long as a Read Burst is in progress, meaning CKE should be kept high until the burst operation is finished. Therefore Active Power-Down mode entry after a Read or Read with Auto-Precharge command is allowed after RL + BL/2 is satisfied.

Active Power-down mode entry is prohibited as long as a Write Burst and the internal write recovery is in progress. In case of a write command, active power-down mode entry is allowed when WL + BL/2 + tWTR is satisfied.

In case of a write command with auto-precharge, power-down mode entry is allowed after the internal precharge command has been executed, which WL + BL/2 + WR is starting from the write with auto-precharge command. In case the DDR2 SDRAM enters the *Precharge Power-down* mode.

## Active Power-Down Mode Entry and Exit after an Activate Command

# Active Power-Down Mode Entry and Exit after a Read Burst: RL = 4 (AL = 1, CL = 3), BL = 4

the MRS, address bit A12.

Active Power-Down Mode Entry and Exit after a Write Burst: WL = 2, tWTR = 2, BL = 4

the MRS, address bit A12.

## Precharge Power Down Mode Entry and Exit

## **No Operation Command**

The No Operation Command should be used in cases when the SDRAM is in an idle or a wait state. The purpose of the No Operation Command is to prevent the SDRAM from registering any <u>unwanted commands</u> <u>between operations</u>. A No Operation Command is registered when CS is low with RAS, CAS, and WE held high at the rising edge of the clock. A No Operation Command will not terminate a previous operation that is still executing, such as a burst read or write cycle.

### **Deselect Command**

The Deselect Command performs the same function as a No Operation Command. Deselect Command occurs when CS is brought high, the RAS, CAS, and WE signals become don't care.

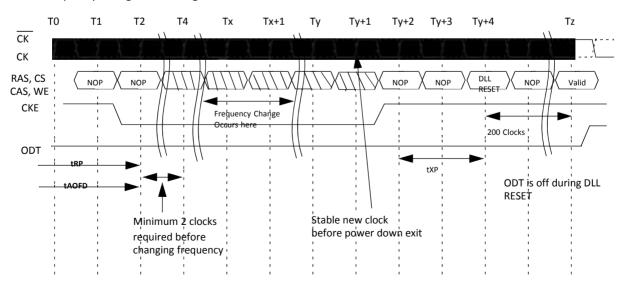

# **Input Clock Frequency Change**

During operation the DRAM input clock frequency can be changed under the following conditions:

- a) During Self-Refresh operation

- b) DRAM is in precharged power-down mode and ODT is completely turned off.

The DDR2-SDRAM has to be in precharged power-down mode and idle. ODT must be already turned off and CKE must be at a logic "low" state. After a minimum of two clock cycles after tRP and tAOFD have been satisfied the input clock frequency can be changed. A stable new clock frequency has to be provided, before CKE can be changed to a "high" logic level again. After tXP has been satisfied a DLL RESET command via EMRS has to be issued. During the following DLL re-lock period of 200 clock cycles, ODT must remain off. After the DLL-re-lock period the DRAM is ready to operate with the new clock frequency.

Clock Frequency Change in Precharge Power Down Mode

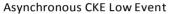

# **Asynchronous CKE Low Event**

DRAM requires CKE to be maintained "high" for all valid operations as defined in this data sheet. If CKE asynchronously drops "low" during any valid operation DRAM is not guaranteed to preserve the contents of the memory array. If this event occurs, the memory controller must satisfy a time delay (tdelay) before turning off the clocks. Stable clocks must exist at the input of DRAM before CKE is raised "high" again. The DRAM must be fully reinitialized as described the initialization sequence starting with step 4.

The DRAM is ready for normal operation after the initialization sequence. The minimum time clocks needs to be ON after CKE asynchronously drops low (the  $t_{delay}$  timing parameter) is equal to tIS + tCK + tIH.

## **Command Truth Table**

|                              | С                 | KE               |    |     |     |    | BA0                   |                       |             |         |        |

|------------------------------|-------------------|------------------|----|-----|-----|----|-----------------------|-----------------------|-------------|---------|--------|

| Function                     | Previous<br>Cycle | Current<br>Cycle | CS | RAS | CAS | WE | -<br>BAx <sup>9</sup> | Axx <sup>9</sup> -A11 | A10         | A9 - A0 | Notes  |

| (Extended) Mode Register Set | н                 | н                | L  | L   | L   | L  | ВА                    | O                     | P Code      | !       | 1,2    |

| Refresh (REF)                | н                 | Н                | L  | L   | L   | Н  | Х                     | Х                     | Х           | х       | 1      |

| Self Refresh Entry           | н                 | L                | L  | L   | L   | Н  | Х                     | Х                     | Х           | Х       | 1,8    |

| C 16 D C . 1 E .:            |                   |                  | Н  | Х   | Х   | Х  | ,,                    | .,                    | .,          | v       | 4.70   |

| Self Refresh Exit            | L                 | Н                | L  | Н   | Н   | Н  | Х                     | X                     | Х           | Х       | 1,7,8  |

| Single Bank Precharge        | Н                 | Н                | L  | L   | Н   | L  | ВА                    | Х                     | L           | Х       | 1,2    |

| Precharge all Banks          | Н                 | Н                | L  | L   | Н   | L  | Х                     | Х                     | Н           | Х       | 1      |

| Bank Activate                | Н                 | Н                | L  | L   | Н   | Н  | ВА                    | Rov                   | Row Address |         | 1,2    |

| Write                        | Н                 | Н                | L  | Н   | L   | L  | ВА                    | Column                | L           | Column  | 1,2,3, |

| Write with Auto Precharge    | Н                 | Н                | L  | Н   | L   | L  | ВА                    | Column                | Н           | Column  | 1,2,3, |

| Read                         | Н                 | Н                | L  | Н   | L   | Н  | ВА                    | Column                | L           | Column  | 1,2,3  |

| Read with Auto-Precharge     | Н                 | Н                | L  | Н   | L   | Н  | ВА                    | Column                | Н           | Column  | 1,2,3  |

| No Operation                 | Н                 | Х                | L  | Н   | Н   | Н  | Х                     | Х                     | Х           | Х       | 1      |

| Device Deselect              | Н                 | Х                | Н  | Х   | Х   | Х  | Х                     | Х                     | Х           | Х       | 1      |

|                              |                   |                  | Н  | Х   | х   | Х  |                       | .,                    | .,          |         |        |

| Power Down Entry             | Н                 | L                | L  | Н   | Н   | Н  | Х                     | Х                     | Х           | Х       | 1,4    |

|                              |                   |                  | Н  | Х   | х   | Х  |                       | .,                    | .,          |         |        |

| Power Down Exit              | L                 | Н                | L  | Н   | Н   | Н  | Х                     | X                     | X           | Х       | 1,4    |

NOTE 1 All DDR2 SDRAM commands are defined by states of CS, RAS, CAS, WE and CKE at the rising edge of the clock. NOTE 2 Bank addresses BAO, BA1, BA2 (BA) determine which bank is to be operated upon. For (E)MRS BA selects an (Extended) Mode Register.

NOTE 3 Burst reads or writes at BL=4 cannot be terminated or interrupted. See sections "Reads interrupted by a Read" and "Writes interrupted by a Write" in section 2.6 for details.

NOTE 4 The Power Down Mode does not perform any refresh operations. The duration of Power Down is therefore limited by the refresh requirements outlined in section 2.9.

NOTE 5 The state of ODT does not affect the states described in this table. The ODT function is not available during Self Refresh. See section 2.4.4.

NOTE 6 "X" means "H or L (but a defined logic level)" NOTE 7

Self refresh exit is asynchronous.

NOTE 8 VREF must be maintained during Self Refresh operation.

NOTE 9 BAx and Axx refers to the MSBs of bank addresses and addresses, respectively, per device density.

## Clock enable (CKE) truth table for synchronous transitions

|                            | CKE                               |                                   | Command (N) <sup>3</sup>         |                            |                  |

|----------------------------|-----------------------------------|-----------------------------------|----------------------------------|----------------------------|------------------|

| Current State <sup>2</sup> | Previous Cycle <sup>1</sup> (N-1) | Current Cycle <sup>1</sup><br>(N) | RAS. CAS. WE. CS                 | Action (N) <sup>3</sup>    | Notes            |

| Power Down                 | L                                 | L                                 | Х                                | Maintain Power-Down        | 11, 13, 14       |

| rower bown                 | L                                 | Н                                 | DESELECT or NOP                  | Power Down Exit            | 4, 8, 11,13      |

| Self Refresh               | L                                 | L                                 | х                                | Maintain Self Refresh      | 11, 14,15        |

| Jen Kenesn                 | L                                 | Н                                 | DESELECT or NOP                  | Self Refresh Exit          | 4, 5, 9, 15      |

| Bank(s) Active             | н                                 | L                                 | DESELECT or NOP                  | Active Power Down Entry    | 4, 8, 10, 11, 13 |

| All Banks Idle             | Н                                 | L                                 | DESELECT or NOP                  | Precharge Power Down Entry | 4, 8, 10, 11,13  |

| All balls fule             | Н                                 | L                                 | REFRESH                          | Self Refresh Entry         | 6, 9, 11,13      |

|                            | Н                                 | Н                                 | Refer to the Command Truth Table |                            | 7                |

NOTE 1 CKE (N) is the logic state of CKE at clock edge N; CKE (N-1) was the state of CKE at the previous clock edge. NOTE 2 Current state is the state of the DDR2 SDRAM immediately prior to clock edge N.

NOTE 3 COMMAND (N) is the command registered at clock edge N, and ACTION (N) is a result of COMMAND (N). NOTE 4 All states and sequences not shown are illegal or reserved unless explicitly described elsewhere in this document.

NOTE 5 On Self Refresh Exit DESELECT or NOP commands must be issued on every clock edge occurring during the  $t_{XSNR}$  period. Read commands may be issued only after  $t_{XSRD}$  (200 clocks) is satisfied.

NOTE 6 Self Refresh mode can only be entered from the All Banks Idle state. NOTE

7 Must be a legal command as defined in the Command Truth Table.

NOTE 8 Valid commands for Power Down Entry and Exit are NOP and DESELECT only. NOTE 9

Valid commands for Self Refresh Exit are NOP and DESELECT only.

- NOTE 10 Power Down and Self Refresh cannot be entered while Read or Write operations, (Extended) Mode Register Set operations or Precharge operations are in progress. See section Power-down and Self refresh operation for a detailed list of restrictions.

- NOTE 11 tCKEmin of 3 clocks means CKE must be registered on three consecutive positive clock edges. CKE must remain at the valid input level the entire time it takes to achieve the 3 clocks of registration. Thus, after any CKE transition, CKE may not transition from its valid level during the time period of tIS + 2 x tCK + tIH.

- NOTE 12 The state of ODT does not affect the states described in this table. The ODT function is not available during Self Refresh.

- NOTE 13 The Power Down does not perform any refresh operations. The duration of Power Down Mode is therefore limited by the refresh requirements outlined in Refresh command section.

- NOTE 14 "X" means "don't care (including floating around VREF)" in Self Refresh and Power Down. However ODT must be driven HIGH or LOW in Power Down if the ODT function is enabled (Bit A2 or A6 set to "1" in EMR(1)).

- NOTE 15 VREF must be maintained during Self Refresh operation.

# DM truth table

| Name (Functional)                                                               | DM | DQs   | Note |  |  |  |

|---------------------------------------------------------------------------------|----|-------|------|--|--|--|

| Write enable                                                                    | L  | Valid | 1    |  |  |  |

| Write inhibit                                                                   | Н  | Х     | 1    |  |  |  |

| NOTE 1 Used to mask write data, provided coincident with the corresponding data |    |       |      |  |  |  |

## **Absolute maximum DC ratings**

| Symbol                            | rmbol Parameter Rating              |                           | Units | Notes |

|-----------------------------------|-------------------------------------|---------------------------|-------|-------|

| VDD                               | Voltage on VDD pin relative to Vss  | ve to Vss - 1.0 V ~ 2.3 V |       | 1,3   |

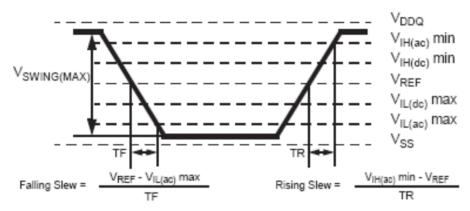

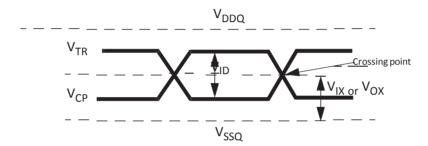

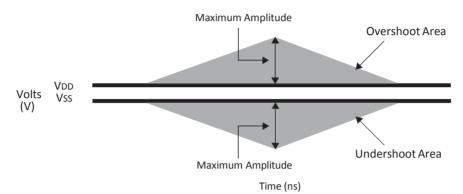

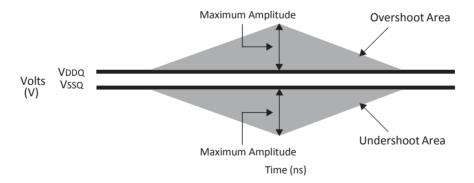

| VDDQ                              | Voltage on VDDQ pin relative to Vss | - 0.5 V ~ 2.3 V           | V     | 1,3   |